## Higher Engineering Mathematics Professor P. N. Agrawal Department of Mathematics Indian Institute of Technology Rookee Lecture No 23 Logic Gates

Hello friends welcome to my lecture on Logic Gates, let us first see what is a logic gate? Computer science at the hardware level involves designing devices to produce appropriate output from the given inputs.

(Refer Slide Time: 0:50)

## Logic Gate

Computer science at the hardware level involves designing devices to produce appropriate output from the given inputs. A logic gate is an electronic circuit that operates one or more input signals to produce an output signal. Gate are digital circuits and often called logic circuits. Gates are represented by symbols, the line entering the symbol from left are inputs, and the line on the right is the output. Placing an small circuit on an input complements or output complements the signal on that line. The input devices are assigned n-bit sequences which are processed by the circuit one bit at a time to produce an output n-bit sequence.

A logic gate is an electronic circuit that operates one or more input signals to produce an output signal. Gates are digital circuits and often called logic circuits. Gates are represented by symbols, the line entering the symbol from left are inputs and the line on the right is the output. Placing a small circuit on an input or output compliments the signal on that line. The input devices are assigned n-bit sequences which are processed by the circuit one bit at a time to produce an output n-bit sequence.

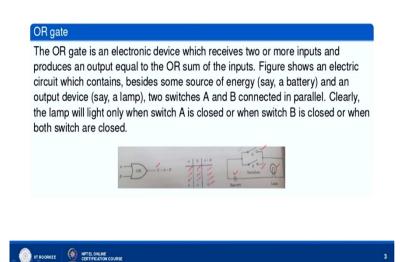

Let us first discuss OR gate, the OR gate is an electronic device which receives two or more inputs like you can see here in this figure two inputs are there shown by A and B and this is your OR gate okay, so two or more inputs and produces an output equal to the or some other inputs, so this is an output, Y is the output okay it is Y=A+B. Figure shows an electric circuit which contains besides some source of energy, now you can see this electric circuit, okay which contains besides some source of say this battery is there this is the source of energy and an output device this is output device okay say a lamp, two switches A and B this is switch A this is switch B two switches A and B are connected in parallel.

Now you can see the light the lamp, the light only when switch A is closed or when switch B is closed or when both switches are closed okay, so you can see switch is closed means we shall denote it by 1 and switch is open will be denoted by bit 0 okay, so the bit one represents that the switch is closed, the bit 0 represents that the which is open. Now if both those which are closed then it will mean that 1+1 okay so that is 1+1you can see here 1+1=1 the lamp will light okay it and then lamp will also light if either one of the two switches to A or B is closed okay.

So suppose A is closed it will be represented by one B is open it is represented by 0, so 1+1 is again 1 okay that means lamb will light okay then A is open to this 0, B is closed it is 1 okay 0+1=1 that means the lamp will light okay and then we have 0+0, 0 and 0 means both the switches are open okay, so when both the switches are open the lamp will not light, so that is shown by 0 okay, so this is OR gate where there are two inputs showing by A and B and there is 1 output, the output will be taking values 1 or 0 if both A and B take values 1,

then it will be 1 output will be 1, if either one of them is 1 then also the output is 1, the output is 0 only when both of them have the value 0.

(Refer Slide Time: 4:06)

| nrananad h             | u an OD actas                         | each of the following pairs of sequences of bits is |

|------------------------|---------------------------------------|-----------------------------------------------------|

|                        |                                       |                                                     |

| (a)110001              | y an OR gate:<br>( <b>b)</b> 10001111 | (c)101100111000                                     |

| (a)110001∱<br>101101 ₺ | (b)10001111<br>00111100               | (c)101100111000<br>000111001101                     |

| (a)110001≜<br>101101₺  | ( <b>b</b> )10001111<br>00111100      | (c)1011100111000<br>000111001101<br> 0       0      |

| (a)110001≜<br>101101₺  | (b)10001111<br>00111100               |                                                     |

| (a)110001≜<br>101101₺  | ( <b>b</b> )10001111<br>00111100      | 1011111101                                          |

Let us look at this example determine how each of the following pairs of sequences of bits is processed by an OR gate, so you can see this is 7 bit sequence 1234567 bit sequence and these are 1+112345678,8-i bit sequence this is 123456789101112 this is 12 bit sequence okay, so this is suppose a and this is b okay so when these are the inputs a and b are inputs the output will be what one plus one will be 1 okay, 1+0 will be 1, 0+1 will be 1, 0+1 will be 1 and then we will have 0+0 okay, 0+0 this is 6 bit sequence right, so0+0=0, 1+1=1.

So that means a plus b will have the bit value 0 only in the case when the corresponding bits have value 0 if either one of them is one or both of them is one then the output will have one is the bit there okay while taking this out. Now here 1+0, 1+0 will be 1, 0+0=0,

0+1=1,1+1=1,1+1=1,1+0=1,1+0=1, so you can see here at the second bit position okay second position both the bits are 0 okay, so we get 0 here, here at the 5<sup>th</sup> position both the bits are 0, so we have 0 otherwise we will always have value 1 and here at the 2<sup>nd</sup> position okay both the bits are 0.

So while getting be some we will have 0 otherwise we will always have one and in this situation also okay at this 11th position both the bits are 0, so the output will contain 0 at 11th position at all other position it will have value 1, so if this be 1+0=1, 0+0=0, 1+0=1, 1+1=1, 0+1=1, 0+1=1, 1+0=1, then 1 and 1 then again one, then again

one then 0 then one okay. So that is the sum when a and b are given by these inputs sequences then the value of y, y=a+b, will have these values.

| Example:Determine |                                                                                |                                                       |  |

|-------------------|--------------------------------------------------------------------------------|-------------------------------------------------------|--|

|                   | X= 1101100101+6100<br>=1101110111<br>Y= 1000110010<br>1100010100<br>1100110110 | IIQIII<br>Z = <u>11011000000</u><br><u>1100110011</u> |  |

|                   | RBE                                                                            |                                                       |  |

(Refer Slide Time: 7:07)

Okay so here we have this, let us see what is output. X will be equal to 11011 okay 110 1100 okay 101 okay and then we have this plus 01001, 010011 okay 0111 okay, so what will be the output you see 1+0 means 1 then 1+1, 10+00 then 1+0=1, okay then 5<sup>th</sup> position is 1 so we have 1, 6<sup>th</sup> position is 0 6<sup>th</sup> position is 1 so we have a 1, 7 position 0 7 position here 0 and here 7 position is 0 okay so we got 0 then 8<sup>th</sup> position is 1 here, you are also 1 so we get 1+1=1, 1+1=1, okay.

Now let us see if I and y okay so why equal to 1 then 000 000 then 11 okay then we have 00 then we have 10 okay and we have a 110 0010 and then 100, so output will be 1+1=1, 0 0+1=1, 0+0=0, 0+0=0, 1+0=1, 1+1=1, 0+0=0, 0+1=1, 1+0=1, 0+0=0, 0 so that will be y okay and that is the output and then you have z, z is 11111 and then we have 12345 a 12345 0s okay there will be a 1100 okay then we have 11 and then we have 00 then we have a 11 okay, so output will be 1+1=1, 1+1=1, 101, 101, 111, 0+0=0, 0+0=0, 0+1=1, 0+1=1 okay so that is the output of the OR gate.

(Refer Slide Time: 10:10)

| a can be extended to more than two inputs. a three input OR gate able is shown in the figure below.         |

|-------------------------------------------------------------------------------------------------------------|

| Imput Output   A C X = A + B + C   A C Y = A + B + C   A C OF   B C Y = A + B + C   A OF OF   B C 0   A D D |

| 0 1 1   Pig 34. Symbol for three root 0 0 1   0fl gate 1 0 1   1 0 1 1   1 1 1 1                            |

|                                                                                                             |

Now let us extend this idea to more than two inputs, so suppose this is the situation here there are 3 inputs you can see ABC okay and this is OR gate, so the output is X=A+B+C so suppose A take value 0, B take value 0, C take value 0, then 0+0+0=0 then A take value 0, B take value 1, so 0+0+1=0 this means that only in the case where ABC all take values 0 in every other case, okay the output will be 1, so you can see 000 only this case has value 0 all other cases will have value 1 001 010 011 100 101 110 111 okay so each other case will have the output 1 okay, so that is the situation in the case of three inputs.

(Refer Slide Time: 11:21)

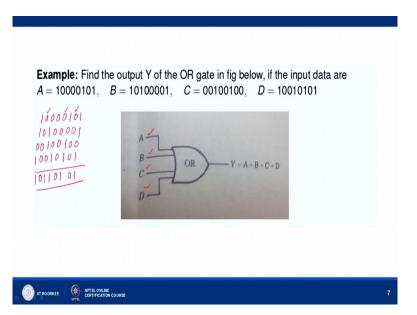

Now, let us consider this case okay we have four inputs ABCD okay so ABC and we have to find what is Y = A + B + C + D, so 10000101 okay then 101 okay 4 000s okay 1 then we have

00 then we have 100 okay, then we have 100 and then we have 100 we have 10 we have 101. You can see, only in the case where all ABC have 0 at the same position okay in every other case the sum will be 1, so you can see 0000 in the 2<sup>nd</sup> position all A and B have 0 and then in the 5<sup>th</sup> position, it will be 5<sup>th</sup> position ABCD all have 0 okay and then in the 7<sup>th</sup> position A has a 0, B has a 0, C has a 0 and D has a 0 okay, so in the 2<sup>nd</sup> position we will have 0, in the 5<sup>th</sup> position we will have 0, in the 7<sup>th</sup> position we will have 0. At all other positions we have 1 so 1011 okay 101 okay so we have 10110101 that is the output Y.

(Refer Slide Time: 13:20)

| AND gate                           |                                                                                                                                                                                                                                                                                                                                                            |

|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| works in a<br>when bot<br>The symb | ble to construct another electronic device called an AND gate which<br>a similar ways as OR gate except that the output only takes the value 1<br>inputs are 1. The output is equal to the AND product of the logic inputs<br>of the gate together with truth table is shown in figure below. Same<br>hold good for an AND gate with more than two inputs. |

|                                    | AND Y-AB (1) A A A A A A A A A A A A A A A A A A A                                                                                                                                                                                                                                                                                                         |

Now, let us consider another electronic device which is called AND gate, it works in a similar manner as an OR gate except that OR output only takes the value 1 when both inputs are one, so when both inputs are one then we will have the output 1 in every other case the output will be 0 this output is equal to the AND products of the logic inputs. The symbol of the gate, this is the symbol okay this is the symbol of the gate and together with the table this is the truth table okay same operation holds good for an AND gate with more than two inputs okay, so if you have more than two inputs the same thing will cover okay, so that means if all inputs will have value 1 then only we will have 1 otherwise we will always have 0 okay.

So like here there are 2 inputs A and B if A and B both have value 1 then you get value 1 in every other case the value of A\*B=0 okay, so if A has value 1, B have value 0 we get 0, if a has value 0, B has value 1 then again A\*B=0 and if A and B both have value 0 then also A\*B=0, so suppose you can show it by electric circuit how it work in an electric circuit,

suppose this is your source battery okay this is lamp okay and these are 2 switches okay connected in series okay.

So if both of them are closed then the lamp will light if anyone of them is open and the other is close then the lamp will not light or if both the switches are open then also the lamp will not light, so when A and B both are closed means A and B both have value 1 okay, if A and B are not both closed then the carry value 0 if one is close the other is open the one which is closed will have a value one the other one which is open will have value 0, so the output will be 1 that is the lamp will light, when both the switches are closed and the lamp will not light if either 1 or both of them of the switches are open okay. So this is the truth table and this is the electric circuit which works according to this AND gate.

(Refer Slide Time: 15:55)

| Example:  | Describe how eac | h pair of the following pairs of sequences of bits is | 3 |

|-----------|------------------|-------------------------------------------------------|---|

| processed | by an AND gate:  | 1 (                                                   |   |

|           | (b)10001111      | (c)101100111000                                       |   |

| 101101    | 00111100         | 000111001101                                          |   |

| (~)  0000 | (6) 00001100     | (c) 000100001000                                      |   |

Now let us consider this case of this example describe how each pair of the following pair of sequences of bits is processed by an AND gate. Early in the situation they are the same position both the input sequences have one okay will have the value 1 otherwise they will always have the value 0, so at the 1<sup>st</sup> position you can see okay about the input sequences have one and at the last position, so that position is position here we have yes at the 6<sup>th</sup> position both input sequences have one hour okay, so at the 6<sup>th</sup> position and at the 1<sup>st</sup> position we will have... the output will contain one at all other position it will contain value 0 okay.

So 10000 and then we have one that is the output of a output in case of b here you can see we have at the 5<sup>th</sup> position both the input sequences have one okay and at the 6<sup>th</sup> position also they have a 1 at all other positions okay... We do not have one at the same position, so

100000010010111111 and otherwise we have 0 okay, so we have c now. Now here we can see at the 4<sup>th</sup> position both the input sequences have 1 and then 5<sup>th</sup>, 6<sup>th</sup>, 7<sup>th</sup>, 8<sup>th</sup>, 9<sup>th</sup> at the 9<sup>th</sup> position both the input sequences have one okay at all other positions they have they do not have one okay at the same position. So1+0, 1\*0=0 then 0 then 1 11 gives 1 then 0 then 000 1000 okay that is the output.

(Refer Slide Time: 18:22)

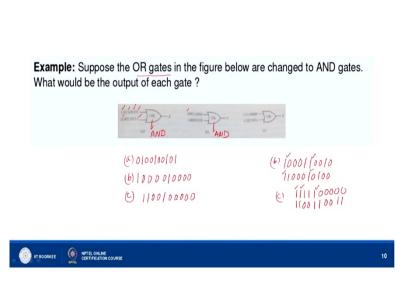

Now let us look at the OR gates here okay suppose the OR gates in the figure below are changed to AND gates okay what would be the output of each sequence? So this OR gates suppose it changed to AND gate okay then what will be the output? So as you let us recall that in the case of AND gate the output has 1 when both the input sequences have one at the same position otherwise the output will always have value 0 okay, so you can see 1011, so at the 2<sup>nd</sup> position we have a 11 then at the position number 5 at position number 5 again and they have a 11, at the 8<sup>th</sup> position they have a 11 okay and then 10 the position they have 11.

So we will have in case a position number 2 as 11 okay so 01 position number 2 has 1, position number 5 has 1 okay and then position number 8 has 1 okay and then position number 10 has 1 okay 11. So if you change OR gate to AND gate here okay then x will have this value okay then in case of b 1<sup>st</sup> position has 11 okay, so if I change this to AND gate okay then we will have one and then we have 000 and then one okay, so we have let us write 1000 3 0s then 11 then we have 00 then we have 10 okay and then we have 11 okay 000 okay 000 10100.

Now, let us see so at 1<sup>st</sup> position we have both bits are one okay so one is there then 0 then 0 then 0 then 0 okay, now you can see 6<sup>th</sup> position, at 6<sup>th</sup> position both the inputs have one okay, so 1 and then 0010, so we have 0000. Now c in case of c what we have this is b part, in case of c part what we have 1111 and we have 1 okay 1 5 times and then 5 times zeros okay. And then 1100 then we have 11 then we have 00 and then we have 11.

Okay so in the 1<sup>st</sup> position and 2<sup>nd</sup> position both the bits are 11 okay at again at the 5<sup>th</sup> position both the bits are 11, so we will have in the 1<sup>st</sup> position in the 2<sup>nd</sup> position and in the 5<sup>th</sup> position. The output will have one at all other positions it will have value 0 okay, so 11 1<sup>st</sup> position 2<sup>nd</sup> position then 00 then 5<sup>th</sup> position you will have 1 and then you will have 00, 00000 so that is the output of each gate if OR gates are changed to AND gates.

(Refer Slide Time: 22:26)

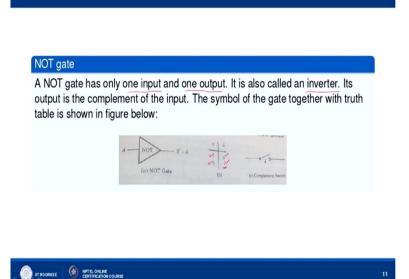

Now, let us say NOT gate, a NOT gate has only one input okay has only one input and one output it is also called an inverter. Its output is the complement of the input, so if the input is 0' of the input will be 1, if the input is 1 the 1'=0, so the output will be 0 okay, so suppose a okay a has value 1 okay then the output will have value 0 if a has value 0 the output will have value 1 okay and this is the symbol for the NOT gate okay the symbol is for NOT gate, y is equal to a complement okay.

So if a denotes the switch okay then if a is one means switch is closed, a conjugate a NOT means the switch is open, a complement, a complement means the switch is open if a has value 0 that means switch is open then A bar which denotes the complement of a will be

having value 1 that is the switch is closed complement switch that will be called complement switch.

(Refer Slide Time: 23:40)

Example: How would a NOT process each of the following sequences ? (a)<u>110001</u>, (b)10001111, (c)101100111000 **Example:** Find  $Y = \overline{A}$ 01001100011 when: (a)A = 10101010, (b)A = 11100111, and (c)A = 00111100. 01110000 (a) 00/110 (A) Y= A= 010101 (b) A= 00011000 (c) A=11000011

So, let us see how would a NOT process each of the following sequences? So we have 110001, so one will be changed to 0 this 1 will be changed to 0 these 3 zeros will change to 111 okay and this will become 0 and here we again this is part a, in part b 1000 okay so 01 will become 0, zeros will change to 111 and we will have 0000 okay and here in the case of c part we will have this as 0 this has 100 11000111 that will become the NOT of a okay.

So now that is the case there, so a part okay that is this will have this value, b part will have this value when NOT process is there okay and when y is equal to  $\dot{a}$ ,  $\dot{a}$  means NOT of a okay so in the case of second example y equal to  $\dot{a}=a'$  so that means 01 okay 01 okay and then 0 then 1 then 0 then 1 okay ones becomes zeros, zeros becomes 1, so 01010101 okay and in the part b this is part a, in the part b similarly,  $\dot{a}=00011000$  and in the c part  $\dot{a}$  will become complement here, so complement of zeros are ones and complement of ones are zeros so 11000011.

## (Refer Slide Time: 25:58)

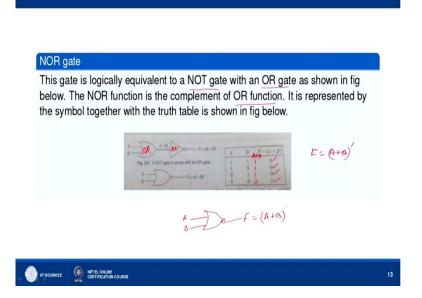

Now NOR gate this gate is logically equivalent to NOT gate with an OR gate okay as shown in the figure below this is OR gate and this is NOT gate okay NOT gate together with an OR gate is NOR gate. The NOR function is the complement of OR function you see when you have a and b okay a or b that is a+b, a+b will have value 1 okay because a and b both have value 1. a+b has value 0 only in the case when a and b both have value 0 otherwise its values is always one, so a+b will have value 1 here 1+0 will have value 1, 0+1 will have a value 1, 0+0 will have value 0 and their complement.

So you can see a+b, a+b will have value 1 here 1 here 1 here 0 here so F is (a+b)' so 1' is 0, 1' is 0 here and 0' is 1 here and now this OR gate and NOT gate can we combine and we show it by this, we put a small circle okay here at the OR gate okay, so this small circle shows that we are considering OR gate together with the NOT gate and that is the NOR gate, so NOR gate has this symbol, this is the symbol for the NOR gate okay and if A and B are 2 inputs okay and F is the output then F = (a+b)' is okay. Refer Slide Time: 28:02)

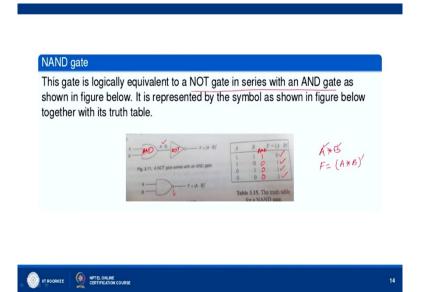

NAND gate, this gate is logically equivalent to NOT gate in series with an AND gate, so AND gate and NOT gate together will give you NAND gate okay so here you see this is AND gate okay and this is NOT gate okay. When A and B are 2 inputs after we apply this AND gate we get A.B okay or A\*B okay and then when NOT gate is applied okay we get (A\*B)' so F becomes (A\*B)' okay and this NOT gate can then be expressed by this symbol A and B are inputs this is your AND gate and we put a small circle here okay that shows AND gate together with NOT gate, NOT gate as I said in the beginning it is shown by a small circle at the input level or at the output level.

So we have...now you see when we have A and B, A\*B has value 1 only in the case when A and B both have value 1 each in every other case has value 0, so A and B are there, so A\*B, A\*B will have value 1 because A and B both have value 1 and in every other case it is value 0 okay and then A star B complement, so 1'=0,0'=1, and 0 here complement is 1 here 0'=1 so that is the truth table for a NAND gate.

Refer Slide Time: 29:49)

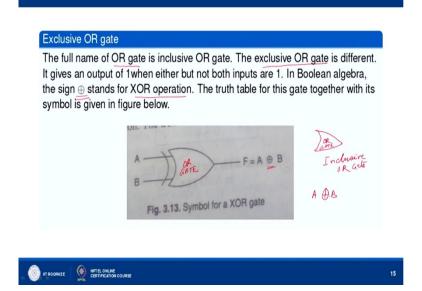

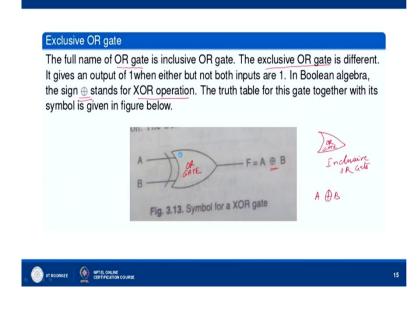

Exclusive OR gate the full name of OR gate, we have earlier considered OR gate this was our OR gate, this was our OR gate okay, so the full name of OR gate is actually this OR gate is inclusive OR gate that is the full name okay the exclusive OR gate is different. It gives an output of 1 when either but not both inputs are one okay, so early in the case where both inputs are 1 in every other case the value of the output will be 1 okay.

So this means that in the case where both inputs are 1 okay we will have value 0 in all other cases 01, 10 or 00 the output will have value 1 okay. In Boolean algebra this exclusive OR gate is shown by this symbol this is states for XOR operation okay. The truth table for this gate together with its symbol is given in figure below okay, so you see this is OR gate okay and this is exclusive OR gate, so this is shown by this, this means that it is exclusive OR gate and when we talk of exclusive OR gate this symbol for XOR operation is this as we have seen, so A circle plus inside the circle plus okay this is symbol for XOR gate.

(Refer Slide Time: 31:35)

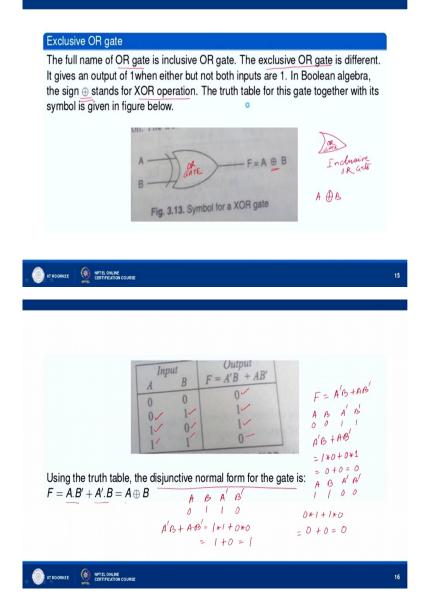

Now you can see here what is the output? A and B both have value suppose 0 we have said here that only in the case where both A and B have value 1 each okay in every other case the value is 1, so A and B okay A and B here both have value 0 okay the output is 0. Here 1 is 0 the other one is 1, so output is 1 okay it gives an output of 1 when either but not both inputs are 1. It gives an output of 1 when either one but not both inputs are 1, so here so this is 0 okay this is 1 then we get one here this is one here it is 0 we get one okay and when we have 11 here we have 0 and when we have 00 that also is 0.

So in the case where A and B both have 0 input okay the output of will again be 0, so only in the case where both inputs are not same okay 00 or 11 in the other situation 01 or 10 the output is 1 otherwise it is 0. Now this output can also be shown by

F = A'B + AB' and we can verify this formula from these values let us say A has value 0, B has value 0, okay then A' will have value 1, B' will have value 1 okay, so A'B + AB', A' has value 1 so 1, A'B means A'\*B, so 1\*0+A, has value 0, B' has value 1, so 0\*1 so we have 1\*0=0 and 0\*1=0 so we get 0+0=0 so we get 0+A and B both have value 1 each okay.

So A has value 1, B has value 1, A' will have value 0, B' will have value 0 okay then A'B=0 so 0\*1 and then AB', A means 1, B' means 0 okay, so 0 star 1=0 okay and 1\*0=0, so we get 0+0 that is equal to 0 okay. Now, let us take the situation where A takes value 0 and B takes value 1, okay this situation 01 and let us show that the value of F is 1, so A'=1, B'=0

Okay now A'B+AB'A'=1, B=1 so 1\*1+1AB'A=0, B'=0 okay 0, 1\*1=1,

0\*0=0 and 1+0=1 okay, so we get the value 1 similarly, we can verify A'B+AB' that this F=1 in the situation when A takes value 1, B takes value 0 we will get the value of F as 1. Now using the truth table the disjunctive normal form for the gate is F=AB'+A'B and we show it by this symbol okay.

(Refer Slide Time: 35:44)

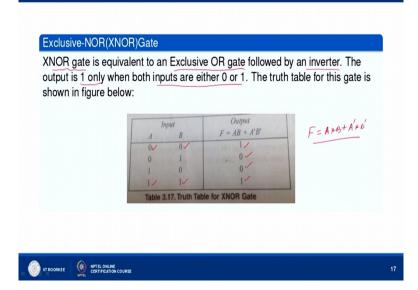

Exclusive NOR gate denoted by XNOR gate, XNOR gate is equivalent to exclusive OR gate okay followed by an inverter. The output is 1 only when both inputs are either 0 or 1. The truth table for this gate is shown here see A and B when both have value 0 then the output is 1 okay and here again when A and B both have input value 1 then we have the wear output as 1. In the other 2 cases when A has value 0, B has value 1, A has value 1, B has value 0 the output value is 0 okay, so you can see the output here is F = A \* B + A' \* B' we can verify this formula for the values of A and B as we verified in the case of exclusive OR gate.

(Refer Slide Time: 36:46)

| (A ⊕ B)′ |                                          |

|----------|------------------------------------------|

| (A XORB) |                                          |

|          | (a) A NOT gate in series with a XOR gate |

## XNOR operation can be written as F = AB + A'B', *A XNOR B* and this is A this is the notation for the operation exclusive OR gate, so this this A exclusive *XOR* gate this is A *XOR* B and this is complement of that, so complement of that becomes *A XNOR* okay so NOT gate in series with XOR gate okay, so XOR gate we have seen this is XOR gate and A and B is the input this gives you A XOR B this is A XOR B and then you put a NOT okay, so that gives A XNOR B. So that is the end of my lecture thank you very much for your attention.