## Analog Electronic Circuits Prof. Pradip Mandal Department of Electronics and Electrical Communication Engineering Indian Institute of Technology, Kharagpur

## Lecture – 30 Common Emitter Amplifier (Contd.) Design Guidelines (Part A)

Hello, so now so, welcome back to this NPTEL online course on Analog Electronic Circuits. This is of course, it is we are having this course for maybe last 2 to 3 weeks, it is continuation of that topic of Common Emitter Amplifier. We have discussed about the theoretical aspect and some of the numerical examples, and in the previous class we could not complete the numerical problems all.

So, today we are discussing some more numerical problems. In fact, in the previous numerical problem we have discussed about, how to find the gain numerically as well as how to analyze the circuit? And, today what will be doing is that in case if we have to design one common emitter amplifier for a given requirement, then how do you proceed and what may be the design guidelines we need to follow. So, that is what will be discussing.

And, also in case if you have see multiple common emitter amplifier cascaded to each other, then how do you find the overall gain? So, these are the two things we do have in mind.

## (Refer Slide Time: 01:57)

So, as I said that this is what we are from in fact, we already have covered significant part of the numerical examples. And, particularly the operating point and then the and it is stability and then finding performance matrices. And, today we are going to discuss about the design guidelines.

And, in case if we have say relatively bigger circuit then how do you proceed to analyze that circuit? So, let me skip a number of slides here.

(Refer Slide Time: 02:51)

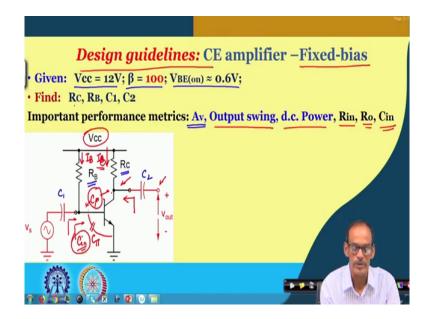

So, we have covered these numerical problems the CE amplifier and then this is where we are going to discuss the design guidelines of common emitter amplifier. And, so, we are going to discuss detail about the design guidelines of common emitter amplifier. And, in case if the topology is fixed and if it is decided to be fixed by us topology.

And, then how do you proceed first thing is that we are assuming that these informations are available particularly the supply voltage it is given to us. Typically and the supply voltage it is given by the customer who requires this circuit. And, also this information may be available particularly, whether the BJT is silicon type or germanium BJT. Based on that we can decide what is the V BE on of the device? And, also we are assuming that the beta of the transistor it is measured and may be 100 or 200 or whatever it is.

So, we assume that these 3 informations are given to us. Whenever then whenever we are talking about we have to design, what do we mean by designing is that finding the value of this bias registers and also these 2 capacitors C 1 and C 2. So, our main task is to find the value of this bias components as well as some guidelines of how to select the value of C 1 and C 2?.

And, of course, the requirement here probably it will be in terms of the gain of the circuit and then the output swing, of the circuit namely what may be the available voltage here or available voltage here without having significant distortion and that is of course, very much important thing. And, then the power dissipation of the circuit. Namely, if the supply voltage is given to us next thing is that the power dissipation it will be decided by how much the quiescent current is flowing through the transistor I C and I B.

So, we can say that I B and I C predominantly I C sorry I C is defining the total current. So, we can say that in the power dissipation it is essentially means that, the value of the collector current. And, then the additional information it may be required is that what may be the input resistance of the circuit, small signal or large signal input resistance, then output resistance of the amplifier and then what may be the input capacitance C in?

So, input capacitance probably we can skip that part for the time being, but just to say that to calculate this C in or to get some information about C in, we require additional information from the device data set is that C pi and C mu.

So, from that we can calculate the what will be the C in? So, as I said that may be in the we will skip this part, because this C mu it is contribution to C in it is through Miller effect. So, we get to cover that Miller effect whenever will be covering that we will discuss about this part.

(Refer Slide Time: 07:04)

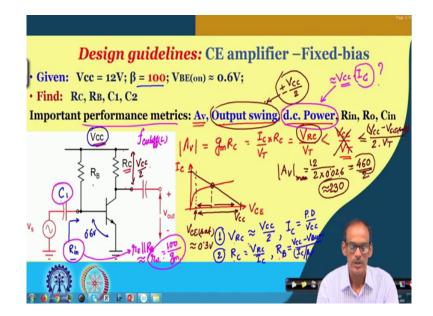

So, then what we are talking about that finding this components based on predominantly from these informations. Now, if you see the voltage gain of the common emitter amplifier A v, we have discussed that it is magnitude it is g m into R C. And, the g m it is and the quiescent current I C divided by thermal equivalent voltage V T. So, this multiplied by R C what it is giving us that voltage drop D C wise voltage drop across this resistance R C divided by V T.

Now, of course, this upper limit of the drop across this resistance it is defined by this V CC. So, it is hard limit is V CC divided by V T. So, we cannot get gain higher than this one. So, definitely I should say this is higher limit. And, in fact, if you consider drop across this resistance is V CC then the required voltage here it is or rather the voltage here to be 0.

So; obviously, if we make this voltage 0 then output signal swing it will be getting affected. So, this is just to say numerical limit of the gain. Practically, you know if we have to consider output swing and to consider the output swing you may recall the load line and then device characteristic and the operating point.

So, I C versus V CE characteristic curve of the device is say like this, then we do have the load line, which is defined by this V CC point here and then the current here or which is V CC divided by R C. And, this is the operating point. So, lower side we do have a limit of the V CE or output voltage it is V CE sat. So, this V C sat again of course, it depends on the device..

Typically, in the order of say 0.2 or 0.3 volt and then we do have V CC. So, over this limit the V CE voltage or the V out voltage it will be flying. As we are applying signal here the corresponding voltage here it will be flying over this range.

Now, to have a meaningful swing of the signal from this with respect to this quiescent point lower side and upper side, it is better to set this quiescent point at the middle. So, I should say that if the quiescent point it is set at the middle, then we can say drop across this resistance R C instead of this the it is limit it should be rather V CC minus V CE sat divided by 2 and then of course, we have the V T.

So, I should say this is the upper limit of the voltage gain giving importance to the output swing. And, in this case if I say that V C sat is very small and then we can say that upper limit of the voltage gain, we can practically you can say this is 12 volt divided by 2 into V T is 0.026 right.

So, that gives us upper limit how much this may be 4 around 460 something. So, beyond this definitely we cannot get the voltage gain. Let me check whether the numerical value, we obtain for this upper limit is this for 61 fine, 461 is the upper limit, but it is fine. So, based on this information and of course, if we do so, the output swing, this output swing it is becoming V CC approximately V CC by 2 plus minus with respect to the quiescent point, ignoring of course, this V C sat assuming this is very small.

So, yes though we do have good swing and then we can have a very decent gain here and this is 6 6 divided by 2 2 1 4 sorry this by 2 rather. So, it is in the order of 231 or so yeah around 230 ok. So, now to get this 230 again, what you have to do that drop across this resistance is we are allocating this voltage drop close to V CC by 2. Now, next thing is that the power dissipation. So, based on this power dissipation information given to us, we can find the value of this current, because we can say this power dissipation it is approximately equal to V CC multiplied by D I C quiescent current of the collector terminal.

So, if the power dissipation is given to us since we know this V CC. So, from that we can find what will be the corresponding I C?. So, then if I know this I C, if I know the drop across this V RC equals to V CC by 2 then I can find what will be the R C?.

So, what is the sequence of finding different parameters, first of all we can set the drop across this R C, in the order of or very close to V CC by 2, that will be giving us good gain as well as output swing. Note that our target probably the again it is not specified it may be say that the gain may be as high as possible and for that to make a balance between this gain and output swing we can take this one.

So, the first thing is that a drop across this one we can take half of the supply voltage. And, then from power dissipation we can find what will be the current quiescent current. So, that is the power dissipation divided by V CC. So, then next thing is that we can find the value of R C which is of course, V RC divided by I C.

And, then from the information of the beta we can find what will be the I B and from that we can calculate what will be the R B. R B equals to V CC minus V BE on divided by I B and I B it is I C divided by the beta. So, from that we can find what will be the value of this element. In fact, this voltage drop it is very close to 0.6.

So, in you may ignore even 0.6 for approximate calculation with respect to 12 volt and that gives you the value of R B. And, from that we obtained the R B and R C and to find the coupling capacitor a signal coupling capacitor or d c, d e coupling capacitor say C 1. We need

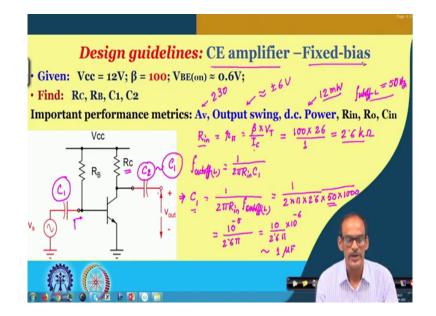

to find what is the input resistance R in and you may recall in our previous example. So, if the collector current it was in the order of you know it was 2 milliampere.

So, the corresponding R in it was. So, R in it was r pi in parallel with R B, which is approximately equals to r pi and r pi equals to beta, which is say 100 divided by g m. So, from that you can of course, the g m we know. So, once we obtain say R C R B then we can find the corresponding r pi. And, then r pi gives us the input resistance R in and from that we can calculate this C 1, because the depending on this value of this R and C or time constant, we can find the we can get the lower cutoff frequency.

So, to be more precise to get meaningful value of this C 1, we require additional information about the performance requirement, namely the lower cutoff frequency. So, if I know that if f cut off L lower cutoff frequency from that we can say that what will be the C 1. So, let me consider that this parts are given to us next thing is that how do we find the C 1? So, let me clear it and then we assume that I C it is known to us.

(Refer Slide Time: 17:47)

Then, R in approximately equal to r pi which is beta divided by g m which is I C divided by V T. And, if I consider I C is say 1 milliampere as a special case or one case and beta is say 100. So, from that we can say that beta multiplied by 26 millivolt divided by 1 milliampere. So, this gives us 2.6 k all right.

And, the lower cutoff frequency f cutoff L equals to 1 by 2 pi R in into C 1, where C 1 is this one. Now, if I consider this value of this R in. So, from that we can see or we can rearrange this equation saying that C 1 equals to 1 by 2 pi R in f cut off right. And, suppose this R in it is say around 25 or 26 k and say lower cutoff frequency is a say 50 Hertz. So, then what may be the value of this C 1? Let us see 1 divided by 2 into pi into R in is 2.6 k into say 50. So, k is 1000 you have to write here yes.

So, we do have 100 here. So, this is 1 by or rather 10 to the power minus 5 divided by 2.6 pi or you can say that this is 10 divided by 2.6 into pi into 10 to the power minus 6 farad, or you can say in the order of say micro farad to get a lower cutoff frequency of 50 Hertz. So, that gives you an idea that for a typical example case the C 1 should be in the order of micro farad.

In fact, the other coupling capacitor may be in the same order assuming that this resistance and input resistance there and also the output resistance here coming from the next stage, or I should say the input resistance of the next stage is may be in the same order of this input resistance. And, hence we can say that C 2 it is also in the order of C 1.

So, what we have done here it is that we got guidelines that, how to design this C amplifier to get a decent performance? Namely, the gain here it is whatever the 20 around 230 and then output swing it is around plus minus 6 volt. And, then power dissipation for say 1 milliampere of current here it is 1 milliampere and 12. So, in the order of or close to 12 milli Watt ok.

And, the cutoff frequency f cut off particularly lower cut off frequency is equal to 50 Hertz right, for that at least we learn how to design the circuit. Let us see the similar kind of guidelines can be followed for CE amplifier with self-bias circuit.

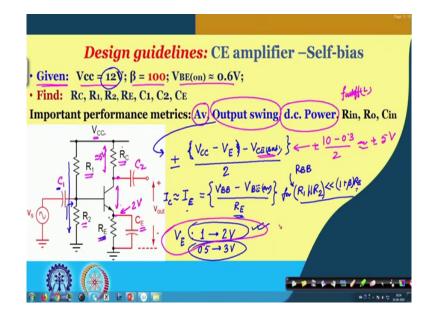

(Refer Slide Time: 22:29)

So, here we do have self-bias and here again we are assuming that these informations are given to us namely, the supply voltage is given to us V BE on it is coming from the data set, the beta also may be coming from the datasheet or it may be you can use multi meter or by some other means to find the value of beta.

So, here we are assuming that this informations are is given to us, we need to find the value of different components namely the resistances here and the capacitor. So, we do have the C 1 C 2 and in addition to that this bypass emitter bypass capacitor C E. And, here of course, we do have the important informations are like this power dissipation also. And, maybe the lower cutoff frequency, if you if this information is provided then it will be better to find the value of this C 1, C 2 and in fact, C E you also.

Now, compared to the previous circuit they approach it will be similar, but you need to understand that the entire V CC voltage it is not available for this collector. So, we do have V CE requirement, V CE sat minimum V CE sat requirement lower side, in addition to that there is a voltage d c voltage require there. Note that while we are connecting the C E and if we are applying a signal here the voltage here it will be d c.

So, this d c voltage it depends on how much the value of this R E we are taking and how much the current emitter current or collector current is flowing through the device. Now, since the voltage drop at this node, it is restricting the limit of this collector voltage of the transistor, then definitely higher the emitter voltage will get lower swing.

So, I should say now the available voltage for output signal it is V CC minus V E emitter voltage divided by. So, this is the; this is the voltage of course, I need to consider the other part also V CE sat. And, then this is the entire swing available to us that divided by 2 may be the possible signal swing. So, plus minus this is the swing.

Now, if I take higher value of this V E and that reduces the swing. On the other hand if I reduce this voltage at this node, which means that the value of this R E it is also getting reduced and then you may recall that the role of this R E, namely the collector current expression it is V BB minus V BE on divided by the I should say not collected a to be more precise the emitter current, divided by this R E.

And, here the assumption is that, assumption is that, R 1 parallel R 2, which you call R BB it is much smaller than 1 plus beta into R E. So, earlier we have discussed this part. And, we may of course, we can we may approximate this is very close to I C. So, why we are looking for this, because we like to make the quiescent point independent of beta?.

So, if I satisfy this condition then we can say that this is independent of beta. And to achieve this one I cannot take this R E small, if I take R E small that will reduce this R BB. So, this is R BB that in turn it will reduce this input resistance, because R BB it is coming in parallel

with whatever r pi you do have. So, if this resistance is smaller for a given value of C 1 the lower cutoff frequency it will be affected.

And, moreover there will be a d c current, if I reduce the value of this R 1 and R 2 then there will be d c current flow and that may increase the power dissipation. So, these 2 are having some trade off the namely the output swing and the value of this R E 2, which is playing the role to stabilize the operating point. And, the thumb rule it is that typically if the supply voltage is say 12 volt, the emitter voltage V d c emitter voltage we can take in the order of 1 to 2 volts.

So, the this does not mean that if you violate this range you may be having severe problem, sometimes we may go lower side even 0.5 volt it may be going towards even 3 volt, but we suggest that may be this may be a good choice. So, we can decide on this one. And, then if we have say 12 volt supply. So, from that if I use say if you use say this is the emitter voltage. So, then the output swing it becomes 10 minus 0.3 divided by 2 approximately it is plus minus 5 volt that is fairly good.

So, once we decide that the output swing we want it should be 5 volt this is a 2 volt, then naturally the drop across this resistance it is also getting fixed, because this is the we like to say this operating point almost at the middle. So, ignoring this V C sat part compared to 12 minus 2 10 volt, we can say that this voltage in it may be 5 volt.

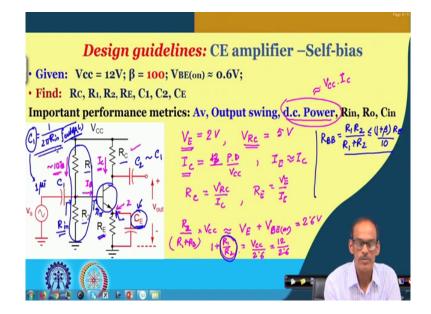

(Refer Slide Time: 29:50)

So, that gives us 2 information; the first of all the V E, we are suggesting to take in the range of 1 to 2 volt as an example if I take say 2 volt, then V RC drop across this resistance R C. So, that is 10 divided 10 minus 2 minus 0.3 by 2. So, we can say that this is also in the order of say 5 volt and then next thing is that the power dissipation.

So, typically whatever the current it will be flowing here I C the current base current it will be 2 order magnitude lower and we like to take this current may be in the order of one order magnitude higher than the I B. So, still this current the current flowing through the bias circuit lower much lower than this I C. So, the power dissipation still it may be considered as it is getting dominated by V CC and I EC.

So, from the power dissipation we can find what will be the value of this I C. And, that is the 12 divided by sorry then this will be power dissipation divided by the 12 volt V CC ok. So,

once we have emitter voltage the voltage drop across R C and then I C which is also approximately equal to I E so.

Now, we can directly get the value of R C and R E. So, V RC divided by I C and R E equals to V E divided by I E ok. So, now, we obtain this to next thing is that these 2 resistances R 1 and R 2 should be such that, the voltage coming here it should be consistent with the require 2 volt here. So, we want this voltage drop here which is R 2 divided by R 1 plus R 2 multiplied by V CC.

So, that is the d c voltage here before we connect the transistor base. So, we can approximate that this voltage it will be very close to whatever the require voltage here, which is the emitter voltage plus V BE on namely in this case this is 2.6 volt.

So, from that we can say that the R 1 R 2 ratio can be obtained right. In other words you can say that 1 plus R 1 divided by R 2 equals to V CC divided by 2.6 12 divided by 2.6. So, that gives us the ratio of R 1 and R 2. So, either from this ratio and this information you can get the value of R 1 and R 2 or we can use the other the additional information we have discussed that R BB, which is equal to R 1 in parallel with R 2, this should be much lower than one plus beta into R E, R E we already obtained.

And, typically we can see that this is less than or equal to 1 10th of this. So, using this guidelines this is R E. So, using these guidelines and the information we obtain here we can find the value of R 1 R 2. So, now we obtain all the bias registers, next thing is that the C 1. So, if you see the input capacitance of this circuit it is in case C E it is dominating. So, for the signal the input resistance it will be the R 1, parallel R 2 in parallel with the R pi. So, this circuit is having input resistance of R pi.

So, from that we can get the R in. Now, similar to the fixed bias circuit we can find the expression of C 1 equals 2 1 by 2 pi R in, then the cutoff frequency, lower cutoff frequency. And so, for a give for the value of this for a given value of this lower cutoff frequency and then R in. Since, this resistance may be in the order of r pi, again this register the value of this

capacitor C 1, it may be similar to whatever previously discussed value of the C 1. So, again this may be in the order of micro farad.

So, likewise the C 2 also it will be in the same order of C 1. Whereas, this C E, it will be having another role to play to define the lower cutoff frequency. And, the lower cutoff frequency decided or defined by this C E, it is coming from the 1 by g m of this device, because this capacitor it will be seeing the resistance of this circuit which is combination of R E and 1 by g m coming from the transistors looking into the emitter. So, the C E on the other hand it can be defined by that and it is expression it will be similar.

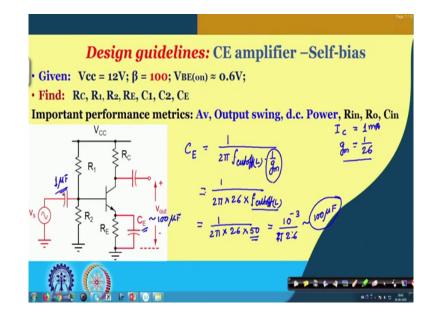

(Refer Slide Time: 36:57)

So, let me clear and then write it about the expression of C E need to be followed. So, C E it is 1 by 2 pi then the f lower cutoff frequency, and then of course, the resistance which is 1 by g m of the transistor. So, we have seen that this 1 by g m it is for say 1 milliampere of current

1 by g m it will be the resistance is very small. As an example here if I consider I C equals to say 1 milliampere, then g m equals to it is 1 by 26, because thermal equivalent voltage it is 26 millivolt.

So, that gives us with this information the expression the C E, it is 1 by 2 pi then g m it is 1 by g m it is. So, g m we do have here yes so, into 26 into f cut off all right. And, you can see here in case if I am looking for lower cutoff frequency of say 50 Hertz, then this will be 1 by 2 pi into 26 into 50.

So, we can write this as 10 to the power minus 3 divided by 2, then you know this is pi then 2.6. So, it is almost in the order of milli farad. So, we can say that this may be coming in the range of milli farad; no it will be 100s of micro farad 100s of micro farad ok.

So, what I like to say that in case if this capacitor value it is in the order of 1 micro farad to support say 50 Hertz, then the required capacitor here capacitance of the C E, it is 100 micro farad. So, the value of this capacitance it will be much higher than this C 1 and C 2 to get the same lower cutoff frequency. So, that is about the overall design guidelines. Let me take a short break and then again will be coming back to cover maybe a little different aspect of the design guidelines.

Thank you.